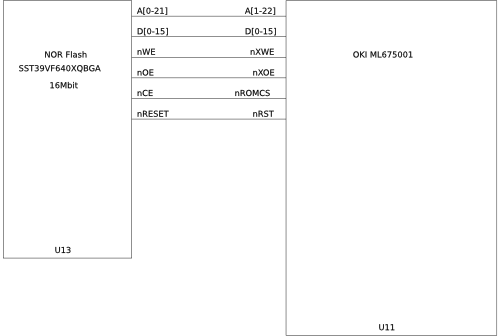

The EB675001DIP has provision for a single NOR flash device. This device typically contains the bootloader and uCLinux image to boot, though it can contain anything the user requires. The flash is implemented as a single sixteen bit wide device, which is selected by use of the nROMCS chip select from the ML675001. This memory appears in bank 25 of the ML675001 memory map.

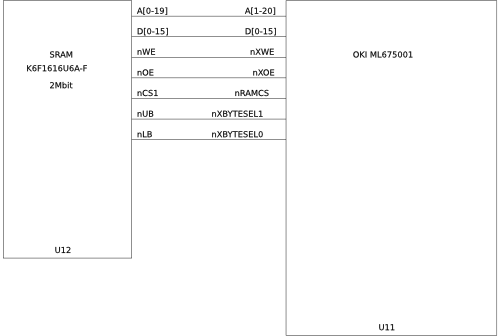

The EB675001DIP has provision for an SRAM device, this is in addition to the 32KB of internal zero wait state memory that is internal to the ML675001. This memory is typically only fitted in the silver configuration of the board. The SRAM is implemented as a single sixteen bit wide device, which is selected by use of the nRAMCS chip select from the ML675001. This memory appears in bank 26 of the ML675001 memory map.

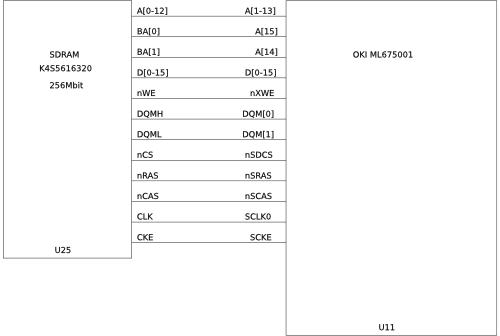

The EB675001DIP has provision for a single SDRAM device with either the default 256MBit capacity or a 512MBit capacity. This memory, where fitted, is accessed using the ML675001 SDRAM controller and appears in bank 24 of its memory map.