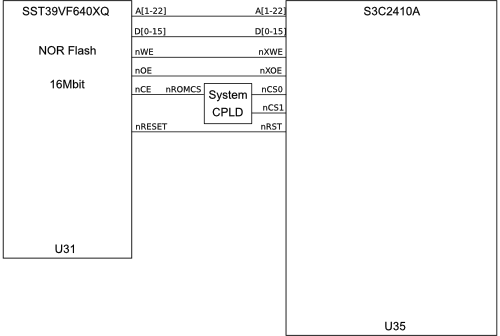

The EB2410ITX has provision for a single NOR flash device. This device typically contains the bootloader and optionally a Linux image to boot, though it can contain anything the user requires. The flash is implemented as a single sixteen bit wide device, which is selected by use of the nROMCS chip select from the system CPLD, nROMCS is derived from nCS<0> and nCS<1> from the S3C2410. This memory appears read only in chip select 0 (0x00000000 to 0x01FFFFFF) and read/write in chip select 1 (0x0C000000 to 0x0DFFFFFF) of the S3C2410 physical memory map.

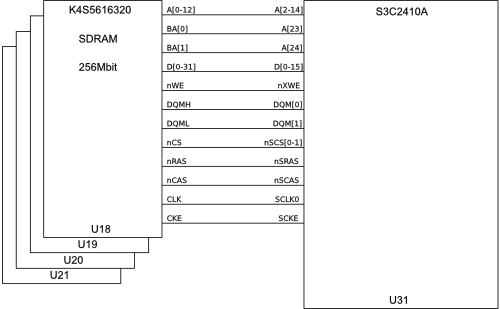

The EB2410ITX has provision for four SDRAM devices with either the default 256MBit capacity or a 512MBit capacity. This memory, where fitted, is accessed using the S3C2410 SDRAM controller and appears in banks six and seven of its physical memory map (0x30000000 and 0x38000000).