The EB675001DIP has a powerful addition to a development system in the form of a user programmable CPLD. This device can be programed to perform a large number of logic functions.

The application notes contain several examples of its flexibility in everything from a simple address decoder to a TV resolution video framebuffer.

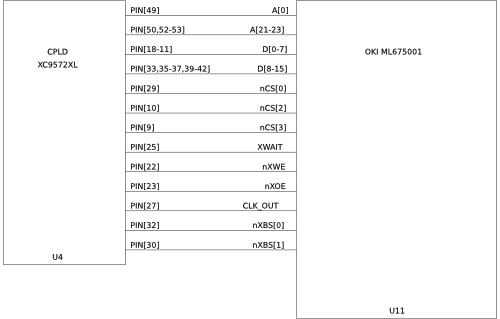

Enough signals are directly connected from the CPU to the CPLD to allow for eight or sixteen bit wide accesses in three chip select regions. CS0 must be treated with care because it is pre decoded by the system CPLD to attach the DM9000 Ethernet controller.

The system wait line is also taken through the user CPLD to allow the CPLD to force I/O wait in CS0 if necessary. More details on the CPLD use and configuration can be found in the User CPLD guide