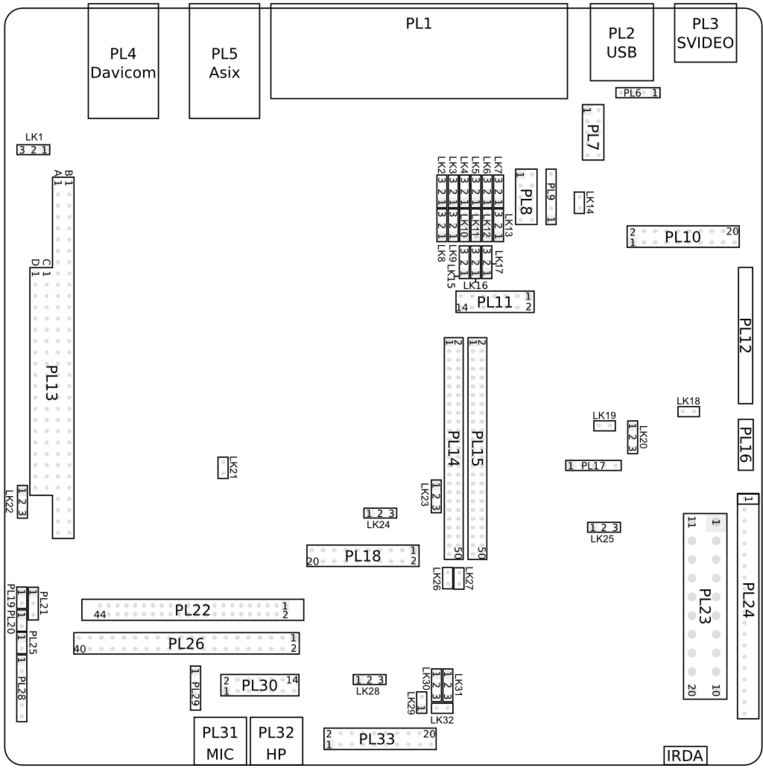

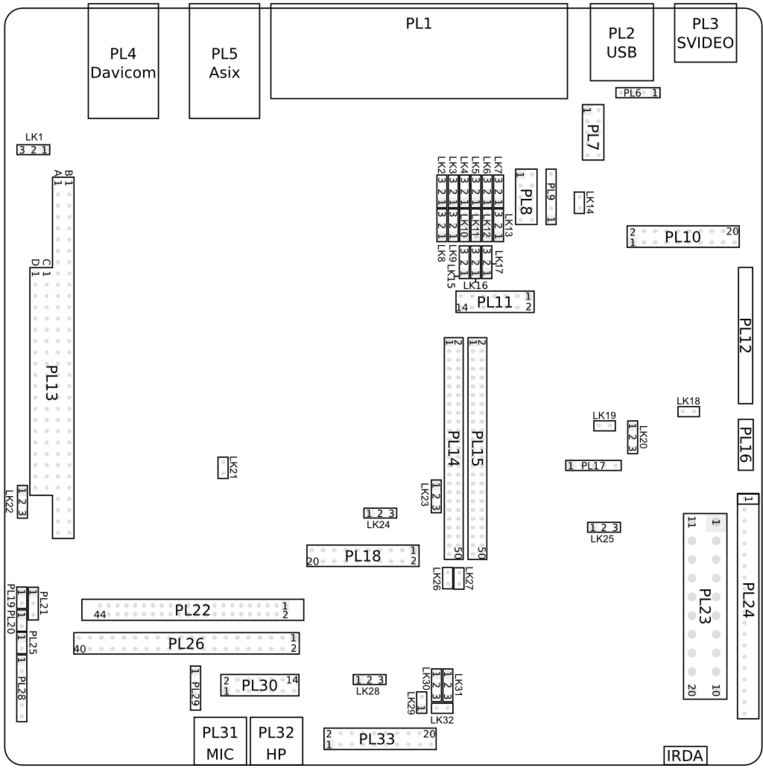

EB2410ITX Connector/Jumper/Pinout list |

| Product | EB2410ITX |

|---|

| Date | 25/03/2008 |

|---|

| Reference | PINLST002 |

|---|

| Author | VRS |

|---|

| Revision | 1.12 |

|---|

|

Contents

©2007 Simtec Electronics

Introduction

This document shows the pinouts for the EB2410ITX. Several

special function pins exist which may be changed to simple GPIO if the

special function is not required. Some pins have more than one special

function which should be taken into account.

The EB2410ITX has a large number of peripherals, not all of these

peripherals are fully realised with physical connectors. For example

there are up to five serial ports available (three from the S3C2410

and two from the superIO controller) and only enough physical space

for a single external 9way D type and a single

internal Box header. The remaining serial ports

are available as LVTTL signals from a pin header array. This is

typical of the design of the EB2410ITX in that we attempt to make all

signals available in a useful form.

Since the EB2410ITX was released SD/MMC has become more popular

than the Smartmedia originally provided for. The SD/MMC port is

available via the 50 way 2mm expansion header and

can be brought to an external connector if desired. These pins were

originally designated for the simple keyboard matrix which cannot be

fully used if SD is required.

The PC104 connector allows for even more expansion

possibilities. There is provision for alternate power supply voltages,

links LK1 and LK22 select

between 3.3V and the more normal 5V.

Video

PL3 - SVideo 4 Pin Mini DIN

| Pin | Designation | Description |

|---|

| 1 | GND | Signal Ground (Y) |

| 2 | GND | Signal Ground (C) |

| 3 | Y | Intensity (Luminance) |

| 4 | C | Color (Chrominance) |

PL1 - Right port VGA

| Pin | Designation | Description |

|---|

| V1 | Red | Red analog video signal |

| V2 | Green | Green analog video signal |

| V3 | Blue | Blue analog video signal |

| V4 | N/C | Not Connected |

| V5 | GND | Signal Ground |

| V6 | GND | Signal Ground |

| V7 | GND | Signal Ground |

| V8 | GND | Signal Ground |

| V9 | VCC | Power |

| V10 | GND | Signal Ground |

| V11 | MD1 | Not Connected |

| V12 | DDC Data | Monitor DDC data |

| V13 | HSync | Horizontal Sync |

| V14 | VSync | Vertical Sync |

| V15 | DDC Clock | Monitor DDC clock |

PL10 - RGB Video expansion header

| Pin | Designation | Description |

|---|

| 1 | 5v | 5 Volt supply |

| 2 | 12v | 12 Volt supply |

| 3 | RED/Y | Red analog video signal |

| 4 | GND | Red signal ground |

| 5 | GREEN/C | Green analog video signal |

| 6 | GND | Green signal ground |

| 7 | BLUE/CVBS | Blue analog video signal |

| 8 | GND | Blue signal ground |

| 9 | CSYNC | Composite sync |

| 10 | GND | Composite sync ground |

| 11 | HSYNC | Horizontal sync |

| 12 | GND | Horizontal sync ground |

| 13 | VSYNC | Vertical sync |

| 14 | GND | Vertical sync ground |

| 15 | GPIO0 | Enable |

| 16 | GPIO1 | |

| 17 | SCL | I2C bus clock |

| 18 | SDA | I2C bus data |

| 19 | 3.3v | 3.3 Volt supply |

| 20 | 3.3v | 3.3 Volt supply |

PL12 - LVDS expansion header

| Pin | Designation | Description |

|---|

| 1 | LCD_SPLY | LCD Power supply |

| 2 |

| 3 | GND | Signal ground |

| 4 | GND |

| 5 | LCDN<0> | LVDS data negative channel 0 |

| 6 | LCDP<0> | LVDS data positive channel 0 |

| 7 | GND | Signal ground |

| 8 | LCDN<1> | LVDS data negative channel 1 |

| 9 | LCDP<1> | LVDS data positive channel 1 |

| 10 | GND | Signal ground |

| 11 | LCDN<2> | LVDS data negative channel 2 |

| 12 | LCDP<2> | LVDS data positive channel 2 |

| 13 | GND | Signal ground |

| 14 | LLCN<1> | LVDS control negative channel 1 |

| 15 | LLCP<1> | LVDS control positive channel 1 |

| 16 | GND | Signal ground |

| 17 | SCL3 | I2C bus clock |

| 18 | SDA3 | I2C bus data |

| 19 | 3V3 | 3.3 Volt supply |

| 20 | GND | Signal ground |

LK20 - Lamp supply voltage select

| Position | Description |

|---|

| 1-2 | 5 Volt output on PL16Pin 1 lamp supply |

| 2-3 | 12 Volt output on PL16Pin 1 lamp supply |

PL16 - Lamp Supply

| Pin | Designation | Description |

|---|

| 1 | LAMP_SPLY | Lamp supply, voltage set by LK20 |

| 2 | GND | Lamp supply ground |

| 3 | TOUT2 | S3C2410 PWM channel 2 |

| 4 | N/C | No connection |

| 5 | GPIO1 | Video GPIO1 from VD9 |

PL15 - 2mm LCD header

| Pin | Designation | Description |

|---|

| 1 | GND | Signal Ground |

| 2 | LCD_SPLY | LCD Power supply |

| 3 | HS | Horizontal Sync |

| 4 | VS | Vertical Sync |

| 5 | VCLK | Vertical Clock |

| 6 | DE/VM | |

| 7 | LEND | Line End |

| 8 | LCD_PWREN | |

| 9 | LCDVF0 | |

| 10 | LCDVF1 | |

| 11 | LCDVF2 | |

| 12 | GND | Signal Ground |

| 13 | 3.3V | 3.3V power |

| 14 | VD0 | Video data Bit 0 (GPC8 - See Note 1) |

| 15 | VD1 | Digital Video data Bit 1 |

| 16 | VD2 | Digital Video data Bit 2 |

| 17 | VD3 | Digital Video data Bit 3 |

| 18 | VD4 | Digital Video data Bit 4 |

| 19 | VD5 | Digital Video data Bit 5 |

| 20 | VD6 | Digital Video data Bit 6 |

| 21 | VD7 | Digital Video data Bit 7 |

| 22 | GND | Signal Ground |

| 23 | VD8 | Digital Video data Bit 8 |

| 24 | VD9 | Digital Video data Bit 9 |

| 25 | VD10 | Digital Video data Bit 10 |

| 26 | VD11 | Digital Video data Bit 11 |

| 27 | VD12 | Digital Video data Bit 12 |

| 28 | VD13 | Digital Video data Bit 13 |

| 29 | VD14 | Digital Video data Bit 14 |

| 30 | VD15 | Digital Video data Bit 15 |

| 31 | GND | Signal Ground |

| 32 | VD16 | Digital Video data Bit 16 |

| 33 | VD17 | Digital Video data Bit 17 |

| 34 | VD18 | Digital Video data Bit 18 |

| 35 | VD19 | Digital Video data Bit 19 |

| 36 | VD20 | Digital Video data Bit 20 |

| 37 | VD21 | Digital Video data Bit 21 |

| 38 | VD22 | Digital Video data Bit 22 |

| 39 | VD23 | Digital Video data Bit 23 |

| 40 | GND | Signal Ground |

| 41 | 3.3V | 3.3V supply |

| 42 | EN_VH_LCD | |

| 43 | LCD_EXP | |

| 44 | ADC2 | Analog channel 2 |

| 45 | GND | Signal Ground |

| 46 | TS_YP | Touch screen YP |

| 47 | TS_YM | Touch screen YM |

| 48 | TS_XM | Touch screen XM |

| 49 | TS_XP | Touch screen XP |

| 50 | GND | Signal Ground |

Note: The video output pins VD0 - VD23 can be

reconfigured to be GPIO direct from the S3c2410 (GPC8 - GPC15 and

GPD0 - GPD15) if video is unused/disabled.

General IO

PL14 - 2mm Aux connector

| Pin | Designation | Description |

|---|

| 1 | 3.3V | 3.3Volt supply |

| 2 | GND | Signal Ground |

| 3 | SMBUS_SDA | SMBUS data |

| 4 | SMBUS_SCL | SMBUS clock |

| 5 | SMBUS_SMALERT | SMBUS alert/IRQ signal. CPU EINT8 or GPF0 1 |

| 6 | GND | Signal Ground |

| 7 | nRESET | Inverted system reset |

| 8 | RESET | System Reset |

| 9 | GND | Signal Ground |

| 10 | 3.3V | 3.3Volt supply |

| 11 | GPF7 / EINT7 | CPU Keyboard Row7 1 |

| 12 | GPF6 / EINT6 | CPU Keyboard Row6 1 |

| 13 | GPF5 / EINT5 | CPU Keyboard Row5 1 |

| 14 | GPF4 / EINT4 | CPU Keyboard Row4 1 |

| 15 | GPF3 / EINT3 | CPU Keyboard Row3 1 |

| 16 | GPF2 / EINT2 | CPU Keyboard Row2 1 |

| 17 | GPF1 / EINT1 | CPU Keyboard Row1 1 |

| 18 | GPF0 / EINT0 | CPU Keyboard Row0 1 |

| 19 | GPE10 / SDDAT3 | CPU Keyboard Col5 or Secure Digital fourth data line 2 |

| 20 | GPE9 / SDDAT2 | CPU Keyboard Col4 or Secure Digital third data line 2 |

| 21 | GPE8 / SDDAT1 | CPU Keyboard Col3 or Secure Digital second data line 2 |

| 22 | GPE7 / SDDAT0 | CPU Keyboard Col2 or Secure Digital first data line 2 |

| 23 | GPE6 / SDCMD | CPU Keyboard Col1 or Secure Digital Command/Data 2 |

| 24 | GPE5 / SDCLK | CPU Keyboard Col0 or Secure Digital Clock 2 |

| 25 | GND | Signal Ground |

| 26 | 3.3V | 3.3Volt supply |

| 27 | SPI_MISO | Primary CPU SPI channel data out |

| 28 | SPI_MOSI | Primary CPU SPI channel data in |

| 29 | SPI_CLK | Primary CPU SPI channel Clock |

| 30 | SPI_CE | SPI CE from S3C2410 GPB5 |

| 31 | GND | Signal Ground |

| 32 | 3.3V | 3.3Volt supply |

| 33 | I2S_AUDIO_SDO | I2S Audio codec serial data out |

| 34 | I2S_AUDIO_CDCLK | I2S Audio codec command/data indicator |

| 35 | I2S_AUDIO_SDI | I2S Audio codec serial data in |

| 36 | I2S_AUDIO_LRCK | I2S Audio codec left/right indicator |

| 37 | I2S_AUDIO_CLK | I2S Audio codec serial data clock |

| 38 | GND | Signal Ground |

| 39 | PWM_TOUT2 | CPU Pulse Width Modulator channel 2 |

| 40 | PWM_TOUT3 | CPU Pulse Width Modulator channel 2 |

| 41 | GND | Signal Ground |

| 42 | ADC0 | Analog digital converter channel 0 |

| 43 | ADC1 | Analog digital converter channel 1 |

| 44 | ADC2 | Analog digital converter channel 2 |

| 45 | GND | Signal Ground |

| 46 | GND | Signal Ground |

| 47 | 5V | 5 Volt supply |

| 48 | 5V | 5 Volt supply |

| 49 | 3.3V | 3.3 Volt supply |

| 50 | GND | Signal Ground |

Note 1: Keyboard rows can be used as GPIO direct from the S3C2410 or as their alternate function is as external interrupt sources.

Note 2: Keyboard column signals can be used as GPIO direct from the S3c2410 or for their alternate use as the Secure Digital port on the S3C2410.

PL13 - PC104

Full details of the PC104 spec can be found on the PC104 website. The pinout here is

duplicated in the user guide and serves as a reference only. Note the

supply voltage to this connector may be changed using LK1 and LK22.

| Pin | Designation | Description |

|---|

| A1 | nIOCHK | |

| A2 | SD7 | Data bit 7 |

| A3 | SD6 | Data bit 6 |

| A4 | SD5 | Data bit 5 |

| A5 | SD4 | Data bit 4 |

| A6 | SD3 | Data bit 3 |

| A7 | SD2 | Data bit 2 |

| A8 | SD1 | Data bit 1 |

| A9 | SD0 | Data bit 0 |

| A10 | IOCHRDY | |

| A11 | AEN | Address enable |

| A12 | SA19 | Address bit 19 |

| A13 | SA18 | Address bit 18 |

| A14 | SA17 | Address bit 17 |

| A15 | SA16 | Address bit 16 |

| A16 | SA15 | Address bit 15 |

| A17 | SA14 | Address bit 14 |

| A18 | SA13 | Address bit 13 |

| A19 | SA12 | Address bit 12 |

| A20 | SA11 | Address bit 11 |

| A21 | SA10 | Address bit 10 |

| A22 | SA9 | Address bit 9 |

| A23 | SA8 | Address bit 8 |

| A24 | SA7 | Address bit 7 |

| A25 | SA6 | Address bit 6 |

| A26 | SA5 | Address bit 5 |

| A27 | SA4 | Address bit 4 |

| A28 | SA3 | Address bit 3 |

| A29 | SA2 | Address bit 2 |

| A30 | SA1 | Address bit 1 |

| A31 | SA0 | Address bit 0 |

| A32 | GND | Signal Ground |

| B1 | GND | Signal Ground |

| B2 | RESET | System reset |

| B3 | ISA VCC1 | Supply |

| B4 | IRQ9 | IRQ 9 |

| B5 | -5V | -5V supply |

| B6 | DRQ2 | |

| B7 | -12V | -12V supply |

| B8 | SRDY | |

| B9 | +12V | +12V supply |

| B10 | KEY(GND) | No pin |

| B11 | nSMEMW | |

| B12 | nSMEMR | |

| B13 | nIOW | Inverted write assert |

| B14 | nIOR | Inverted read assert |

| B15 | nDACK3 | |

| B16 | DRQ3 | |

| B17 | nDACK1 | |

| B18 | DRQ1 | |

| B19 | nREFRESH | |

| B20 | BCLK | |

| B21 | IRQ7 | IRQ 7 |

| B22 | IRQ6 | IRQ 6 |

| B23 | IRQ5 | IRQ 5 |

| B24 | IRQ4 | IRQ 4 |

| B25 | IRQ3 | IRQ 3 |

| B26 | nDACK2 | |

| B27 | TC | |

| B28 | BALE | |

| B29 | ISA VCC2 | |

| B30 | 14MHz CLK | Clock |

| B31 | GND | Signal ground |

| B32 | GND | Signal ground |

| C0 | GND | Signal ground |

| C1 | nSBHE | |

| C2 | LA23 | Latched address bit 23 |

| C3 | LA22 | Latched address bit 22 |

| C4 | LA21 | Latched address bit 21 |

| C5 | LA20 | Latched address bit 20 |

| C6 | LA19 | Latched address bit 19 |

| C7 | LA18 | Latched address bit 18 |

| C8 | LA17 | Latched address bit 17 |

| C9 | nMEMR | MMIO read |

| C10 | nMEMW | MMIO write |

| C11 | SD8 | Data bit 8 |

| C12 | SD9 | Data bit 9 |

| C13 | SD10 | Data bit 10 |

| C14 | SD11 | Data bit 11 |

| C15 | SD12 | Data bit 12 |

| C16 | SD13 | Data bit 13 |

| C17 | SD14 | Data bit 14 |

| C18 | SD15 | Data bit 15 |

| C19 | KEY(GND) | Key |

| D0 | GND | Signal ground |

| D1 | nMEMCS16 | 16 bit memory cycle |

| D2 | nIOCS16 | 16 bit I/O cycle |

| D3 | IRQ10 | IRQ 10 |

| D4 | IRQ11 | IRQ 11 |

| D5 | IRQ12 | IRQ 12 |

| D6 | IRQ15 | IRQ 15 |

| D7 | IRQ14 | IRQ 14 |

| D8 | nDACK0 | |

| D9 | DRQ0 | |

| D10 | nDACK5 | |

| D11 | DRQ5 | |

| D12 | nDACK6 | |

| D13 | DRQ6 | |

| D14 | nDACK7 | |

| D15 | DRQ7 | |

| D16 | ISA VCC2 | Supply |

| D17 | nMASTER | |

| D18 | GND | Signal ground |

| D19 | GND | Signal ground |

LK1 - PC104 Supply 1

| Connection | Description |

|---|

| 1-2 | 3.3V |

| 2-3 | 5V |

LK22 - PC104 Supply 2

| Connection | Description |

|---|

| 1-2 | 3.3V |

| 2-3 | 5V |

PL25 - Reset button

| Pin | Designation | Description |

|---|

| 1 | Reset | System reset should be connected to reset ground momentarily for a reset. |

| 2 | GND | Reset ground |

PL1 - parallel port

This port is either the port provided by the super I/O

controller. If the super I/O option is not fitted a simple parallel

port may be provided by the Asix network controller. This option is

enabled by optional resistor packs RB2, RB4, RB5, RB7

| Pin | Designation | Description |

|---|

| P1 | Strobe | Data strobe |

| P2 | Data0 | First data line |

| P3 | Data1 | Second data line |

| P4 | Data2 | Third data line |

| P5 | Data3 | Fourth data line |

| P6 | Data4 | Fifth data line |

| P7 | Data5 | Sixth data line |

| P8 | Data6 | Seventh data line |

| P9 | Data7 | Eighth data line |

| P10 | ACK | Data acknowledge |

| P11 | BUSY | Device busy |

| P12 | PE | |

| P13 | ATFD | |

| P14 | ERR | Device error |

| P15 | SLCT | |

| P16 | INIT | |

| P17 | SLIN | |

| P18 | GND | Signal Ground |

| P19 | GND | Signal Ground |

| P20 | GND | Signal Ground |

| P21 | GND | Signal Ground |

| P22 | GND | Signal Ground |

| P23 | GND | Signal Ground |

| P24 | N/C | Not connected |

| P25 | GND | Signal Ground |

Networking

PL5 - Asix Ethernet port

| Pin | Designation | Description |

|---|

| 1 | AXTX+ | Transmit positive |

| 2 | AXTX- | Transmit negative |

| 3 | AXRX+ | Receive positive |

| 4 | N/C | No connection |

| 5 | N/C | No connection |

| 6 | AXRX- | Receive Negative |

| 7 | N/C | No connection |

| 8 | N/C | No connection |

PL4 - Davicom Ethernet port

| Pin | Designation | Description |

|---|

| 1 | DMTX+ | Transmit positive |

| 2 | DMTX- | Transmit negative |

| 3 | DMRX+ | Receive positive |

| 4 | N/C | No connection |

| 5 | N/C | No connection |

| 6 | DMRX- | Receive Negative |

| 7 | N/C | No connection |

| 8 | N/C | No connection |

LCD Module

The LCD module interface is distinct from the main LCD video

display, it provides an eight bit parallel interface to LCD

modules, the chip select and address decode is performed by the

system CPLD and allows for direct connection of two HD44780 type

modules with a simple ribbon cable (the second module connection

must be made to use the second enable line).

LK28 - LCD Module voltage select

| Position | Description |

|---|

| 1-2 | 3.3 Volt output on PL33 pin 2 |

| 2-3 | 5 Volt output on PL33 pin 2 |

LK29 - LCD Module VEE select

| Position | Description |

|---|

| 1-2 | LCD module PL33 pin 18 (VEE) is GND |

| Open | LCD module PL33 pin 18 (VEE) is connected to pin 1 |

R225 - LCD module backlight control

Variable resistor which sets the backlight supply (PL33 pin 16) current

R242 - LCD module contrast control

Selects contrast control between LCD Module voltage select LK28 and VEE LK29.

PL33 LCD Module header

| Pin | Designation | Description |

|---|

| 1 | GND | Module ground |

| 2 | LCD Supply | LCD Module voltage set by LK28 |

| 3 | LCD contrast | LCD Module contrast voltage controlled by R242 |

| 4 | LCD_CMD | Command/Data strobe |

| 5 | LCD_RW | Read not write |

| 6 | LCD_E1 | Fist enable |

| 7 | LCD_D0 | First data line |

| 8 | LCD_D1 | Second data line |

| 9 | LCD_D2 | Third data line |

| 10 | LCD_D3 | Fourth data line |

| 11 | LCD_D4 | Fifth data line |

| 12 | LCD_D5 | Sixth data line |

| 13 | LCD_D6 | Seventh data line |

| 14 | LCD_D7 | Eighth data line |

| 15 | 5V | 5 Volt supply |

| 16 | Backlight | Backlight supply current limited by R225 |

| 17 | nRESET_LCD | Inverted LCD reset |

| 18 | VEE | VEE controlled by LK29 |

| 19 | LCD_E2 | Second enable |

| 20 | N/C | Not connected |

IDE

A pair of standard parallel ATA (IDE) channels are

provided. They are presented as on 40 way standard box header

and a second 44 way laptop style connector. The two channels

are buffered and isolated form the rest of the systems busses

but do share a single data buffer, this may cause

issues with some ATA devices (notably cheap CF cards) which do

not properly qualify their data bus usage with their

respective separate read and write strobes.

PL26 - Standard 40 IDE

| Pin | Designation | Description |

|---|

| 1 | nRST | Bus reset |

| 2 | GND | Signal ground |

| 3 | IDE7 | Data bit 7 |

| 4 | IDE8 | Data bit 8 |

| 5 | IDE6 | Data bit 6 |

| 6 | IDE9 | Data bit 9 |

| 7 | IDE5 | Data bit 5 |

| 8 | IDE10 | Data bit 10 |

| 9 | IDE4 | Data bit 4 |

| 10 | IDE11 | Data bit 11 |

| 11 | IDE3 | Data bit 3 |

| 12 | IDE12 | Data bit 12 |

| 13 | IDE2 | Data bit 2 |

| 14 | IDE13 | Data bit 13 |

| 15 | IDE1 | Data bit 1 |

| 16 | IDE14 | Data bit 14 |

| 17 | IDE0 | Data bit 0 |

| 18 | IDE15 | Data bit 15 |

| 19 | GND | Signal ground |

| 20 | KEY | No connection |

| 21 | I_DRQ0 | |

| 22 | GND | Signal ground |

| 23 | I_IOW0 | |

| 24 | GND | Signal ground |

| 25 | I_IOR0 | |

| 26 | GND | Signal ground |

| 27 | I_IORDY0 | |

| 28 | I_CS1 | |

| 29 | I_DACK0 | |

| 30 | GND | Signal ground |

| 31 | I_IRQ_0_b | |

| 32 | nIO16 ->high | |

| 33 | I_A1 | Address bit 1 |

| 34 | nPDIAG | |

| 35 | I_A0 | Address bit 0 |

| 36 | I_A2 | Address bit 2 |

| 37 | nCS0 | Chip select 0 |

| 38 | nCS1 | Chip select 1 |

| 39 | nDASP | |

| 40 | GND | Signal ground |

PL22 - Standard 44 IDE (portable 2mm connector)

| Pin | Designation | Description |

|---|

| 1 | nRST | Bus reset |

| 2 | GND | Signal ground |

| 3 | IDE7 | Data bit 7 |

| 4 | IDE8 | Data bit 8 |

| 5 | IDE6 | Data bit 6 |

| 6 | IDE9 | Data bit 9 |

| 7 | IDE5 | Data bit 5 |

| 8 | IDE10 | Data bit 15 |

| 9 | IDE4 | Data bit 4 |

| 10 | IDE11 | Data bit 11 |

| 11 | IDE3 | Data bit 3 |

| 12 | IDE12 | Data bit 12 |

| 13 | IDE2 | Data bit 2 |

| 14 | IDE13 | Data bit 13 |

| 15 | IDE1 | Data bit 1 |

| 16 | IDE14 | Data bit 14 |

| 17 | IDE0 | Data bit 0 |

| 18 | IDE15 | Data bit 15 |

| 19 | GND | Signal ground |

| 20 | KEY | Not connected |

| 21 | I_DRQ0 | |

| 22 | GND | Signal ground |

| 23 | I_IOW0 | |

| 24 | GND | Signal ground |

| 25 | I_IOR0 | |

| 26 | GND | Signal ground |

| 27 | I_IORDY0 | |

| 28 | I_CS1 | Chip select 1 |

| 29 | I_DACK0 | |

| 30 | GND | Signal ground |

| 31 | I_IRQ_0_b | |

| 32 | nIO16 ->high | |

| 33 | I_A1 | Address bit 1 |

| 34 | nPDIAG | |

| 35 | I_A0 | Address bit 0 |

| 36 | I_A2 | Address bit 2 |

| 37 | nCS0 | Chip select 0 |

| 38 | nCS1 | Chip select 1 |

| 39 | nDASP | |

| 40 | GND | Signal ground |

| 41 | Fused 1.1A +5V | Supply |

| 42 | Fused 1.1A +5V | Supply |

| 43 | GND | Supply ground |

| 44 | Weak 10k pull up | |

PL19 - Hard Disk activity LED

| Pin | Designation | Description |

|---|

| 1 | 5V | 5 Volt supply |

| 2 |

Activity |

Activity line which is driven low and sinks current to light an LED |

Audio

PL31 - MIC in

| Pin | Designation | Description |

|---|

| 1 | GND | Microphone ground |

| 2 | N/C | Not connected |

| 3 | N/C | Not connected |

| 4 | N/C | Not connected |

| 5 |

MIC_IN |

Input for a condensing microphone. |

PL32 - Headphones out

| Pin | Designation | Description |

|---|

| 1 | GND | Headphone ground |

| 2 | HP_RIGHT | Headphone right |

| 3 | SPKR passthrough | Right speaker pass through |

| 4 | SPKR passthrough | Left speaker pass through |

| 5 | HP_LEFT | Headphone left |

PL28 - Speaker/PC beeper

| Pin | Designation | Description |

|---|

| 1 | Speaker - | Speaker negative terminal |

| 2 | Speaker + | Speaker positive terminal |

| 3 | PIC_BEEP | |

| 4 | Speaker + | Speaker negative terminal |

| 5 | PIC_BEEP | |

| 6 | 3.3V | 3.3 Volt supply |

PL29 - CDROM audio

| Pin | Designation | Description |

|---|

| 1 | LEFT line in | CDROM left channel in |

| 2 | GND | Left channel ground |

| 3 | GND | Right channel ground |

| 4 | RIGHT line in | CDROM right channel in |

PL30 - Audio Expansion

| Pin | Designation | Description |

|---|

| 1 | MIC IN | Microphone input |

| 2 | GND | Microphone ground |

| 3 | Line in left | Left line in |

| 4 | GND | Line in ground |

| 5 | Line in right | Right line in |

| 6 | GND | Line in ground |

| 7 | Line out Left | Left line out |

| 8 | GND | Line out ground |

| 9 | Line out Right | Right line out |

| 10 | GND | Line out ground |

| 11 | Headphone left out | Amplified headphone left channel |

| 12 | GND | Headphone ground |

| 13 | Headphone out right | Amplified headphone right channel |

| 14 | GND | Headphone ground |

PL11 - SMBUS,ANALOG,EEPROM set/test

| Pin | Designation | Description |

|---|

| 1 | 3.3V Standby | 3.3 Volt standby |

| 2 | 5V | 5 Volt supply |

| 3 | SMBUS Alert | SMBUS interrupt |

| 4 | CPU_VADJ | Processor voltage adjust |

| 5 | SDA | SM Bus Data |

| 6 | LCD_EXP | |

| 7 | SCL | SM Bus clock |

| 8 | PWM_K_SET | Pulse Width Modulation selection |

| 9 | GND | Ground |

| 10 | K_SET | |

| 11 | EEPROM Write protect | Protect EEPROM |

| 12 | VCC_LCD | LCD supply |

| 13 | VCC_ALIVE | Supply enable |

| 14 | V0_SET | |

Power

PL20 - Power button

| Pin | Designation | Description |

|---|

| 1 | PWR_BTN | Momentary connection to ground toggles power state using PMU |

| 1 | GND | Power button ground |

PL21 - Power LED

| Pin | Designation | Description |

|---|

| 1 | +ve Power LED | Power LED anode |

| 2 | GND | Ground |

| 3 | -ve PWR LED | Power LED cathode |

PL23 - ATX power connector

| Pin | Designation | Description |

|---|

| 1 | 3.3V | 3.3 Volt supply |

| 2 | 3.3V | 3.3 Volt supply |

| 3 | GND | Power Ground |

| 4 | 5V | 5 Volt supply |

| 5 | GND | Power Ground |

| 6 | 5V | 5 Volt supply |

| 7 | GND | Power Ground |

| 8 | DC-OK | Power OK |

| 9 | 5V standby | 5 Volt standby supply |

| 10 | 12V | 12 Volt supply |

| 11 | 3.3V | 3.3 Volt supply |

| 12 | -12V | Negative 12 Volt supply |

| 13 | GND | Power Ground |

| 14 | PSU-EN | Supply enable |

| 15 | GND | Power Ground |

| 16 | GND | Power Ground |

| 17 | GND | Power Ground |

| 18 | -5V | Negative 5 Volt supply |

| 19 | 5V | 5 Volt supply |

| 20 | 5V | 5 Volt supply |

PL24 - Aux SIL power connector

| Pin | Designation | Description |

|---|

| 1 | 3.3V | 3.3 Volt supply |

| 2 | 3.3V | 3.3 Volt supply |

| 3 | GND | Power Ground |

| 4 | GND | Power Ground |

| 5 | +5V | 5 Volt supply |

| 6 | +5V | 5 Volt supply |

| 7 | 5V standby | 5 Volt standby supply |

| 8 | ALIVE | |

| 9 | +12V | 12 Volt supply |

| 10 | GND | Power Ground |

| 11 | GND | Power Ground |

| 12 | -12V | Negative 12 Volt supply |

| 13 | -5V | Negative 5 Volt supply |

| 14 | GND | Power Ground |

| 15 | PWM | |

| 16 | 5V_EN | |

| 17 | 3V_EN | |

| 18 | PSU_ON | |

| 19 | PG | |

| 20 | IO/VIN | |

LK19 - ATX power always on

| Position | Description |

|---|

| 1-2 | Force power on at startup |

| Open | Normal behaviour |

Debug and JTAG

PL18 - JTAG multi ICE

| Pin | Designation | Description |

|---|

| 1 | 3.3V | 3.3 Volt supply |

| 2 | 3.3V | 3.3 Volt supply |

| 3 | nTRST | Inverted tap reset |

| 4 | GND | Signal ground |

| 5 | TDI | Tap data in |

| 6 | GND | Signal ground |

| 7 | TMS | Tap |

| 8 | GND | Signal ground |

| 9 | TCK | Tap clock |

| 10 | GND | Signal ground |

| 11 | RCLK | Returned clock |

| 12 | GND | Signal ground |

| 13 | TDO | Tap data out |

| 14 | GND | Signal ground |

| 15 | nSRST | Inverted system reset |

| 16 | GND | Signal ground |

| 17 | N/C | Not connected |

| 18 | GND | Signal ground |

| 19 | N/C | Not connected |

LK21 - NOR ROM write protect

| Position | Description |

|---|

| 1-2 | NOR Flash write enabled |

| Open | Write inhibited, Pin 1 is the ROM WE line suitable for use with some JTAG accelerators |

LK14 - Non volatile RAM use

| Position | Description |

|---|

| 1-2 | Non volatile memory settings used by bootloader |

| Open | Non volatile memory settings Ignored by bootloader |

LK18 - Alternate Config

| Position | Description |

|---|

| 1-2 | Alternate configuration used by bootloader |

| Open | Alternate configuration Ignored by bootloader |

PL17 - PMU programming header

This header allows the PIC device which acts as the system

power manager to be reprogrammed, this is not generally

useful. Please contact Simtec support if more information is

required.

| Pin | Designation | Description |

|---|

| 1 | VPP | |

| 2 | VCC_PIC_PGM | |

| 3 | GND | |

| 4 | PGD | |

| 5 | PGC | |

LK25 - PMU programing voltage

| Position | Description |

|---|

| 1-2 | 3V Run |

| 2-3 | 5V Program |

COM1

The external 9 way serial port has been designated COM1, this

port may be easily connected to either the super I/O controller

or the first serial port of the S3C2410 (which is the

default).

PL1 Left port - Serial Port - COM1 RS232

| Pin | Designation | Description |

|---|

| S1 | DCD | Data carrier detect |

| S2 | RX | Receive |

| S3 | TX | Transmit |

| S4 | DTR | Data terminal ready |

| S5 | GND | Ground |

| S6 | DSR | Data set ready |

| S7 | RTS | Request to send |

| S8 | CTS | Clear to send |

| S9 | RI | Ring indicator |

LK2 - Serial power

| Pin | Description |

|---|

| 1 | 3.3V supply |

| 2 | 3.3V supply |

| 3 | 3.3V supply |

LK3 - COM1 RTS Select

| Position | Description |

|---|

| 1-2 | S3C2410 RTS0 on COM1 RTS OUT |

| 2-3 | Super I/O RTS0 on COM1 RTS OUT |

LK4 - COM1 TX Select

| Position | Description |

|---|

| 1-2 | ARM9 TX0 on COM1 TX OUT |

| 2-3 | Nat Semi TX0 on COM1 TX OUT |

LK5 - COM1 RX Select

| Position | Description |

|---|

| 1-2 | ARM9 RX0 on COM1 RX IN |

| 2-3 | NS RX0 on COM1 RX IN |

LK6 - COM1 CTS Select

| Position | Description |

|---|

| 1-2 | ARM9 CTS0 on COM1 CTS IN |

| 2-3 | NS CTS0 on COM1 CTS IN |

LK7 - GND

| Pin | Description |

|---|

| 1 | GND |

| 2 | GND |

| 3 | GND |

COM2 Select

The internal 10 way box header has been designated COM2, this

port may be easily connected to the second serial port of either

the super I/O controller or the S3C2410 (which is the

default). This box header is "PC" internal style and a simple

1:1 IDC to 9 way D lead may be used.

PL7 - Internal serial box header

| Pin | Designation | Description |

|---|

| 1 | DCD | Data carrier detect |

| 2 | DSR | Data set ready |

| 3 | RX | Receive |

| 4 | RTS | Request to send |

| 5 | TX | Transmit |

| 6 | CTS | Clear to send |

| 7 | DTR | Data terminal ready |

| 8 | RI | Ring indicator |

| 9 | GND | Serial ground |

| 10 | NC | Not connected |

LK8 - Serial power

| Pin | Description |

|---|

| 1 | 3.3V |

| 2 | 3.3V |

| 3 | 3.3V |

LK9 - COM2 RTS Select

| Position | Description |

|---|

| 1-2 | ARM9 RTS1 on COM2 RTS OUT |

| 2-3 | Nat Semi RTS1 on COM2 RTS OUT |

LK10 - COM2 TX Select

| Position | Description |

|---|

| 1-2 | ARM9 TX1 on COM2 TX OUT |

| 2-3 | Nat Semi TX1 on COM2 TX OUT |

LK11 - COM2 RX Select

| Position | Description |

|---|

| 1-2 | ARM9 RX1 on COM2 RX IN |

| 2-3 | NS RX1 on COM2 RX IN |

LK12 - COM2 CTS Select

| Position | Description |

|---|

| 1-2 | ARM9 CTS1 on COM2 CTS IN |

| 2-3 | NS CTS1 on COM2 CTS IN |

LK13 - Serial ground

| Pin | Description |

|---|

| 1 | GND |

| 2 | GND |

| 3 | GND |

IR Select

The infra red port may be selected between the second port of

the super I/O controller or the third port of the S3C2410. These

signals are not RS232 level translated and appear as LVTTL open

collector style signals.

PL9 - IRDA FIR

| Pin | Designation | Description |

|---|

| 1 | 3.3v | 3.3 Volt supply |

| 2 | IRRX | Infra red receive |

| 3 | IRRSL | |

| 4 | GND | IR ground |

| 5 | IRTX | Infra red transmit |

PL8 - IR Dongle interface

| Pin | Designation | Description |

|---|

| 1 | IRTX | Infra red transmit |

| 2 | IRRSL1 | |

| 3 | GND | Ground |

| 4 | 5v | 5 Volt supply |

| 5 | IRRSL2 | |

| 6 | NC | Not connected |

| 7 | IRRX | Infra red receive |

| 8 | IRRSL0 | |

| 9 | GND | Ground |

| 10 | nIR_EN | Inverted infra red enable |

NOTE - 9-10 normally made

LK15 - IR TX Select

| Position | Description |

|---|

| 1-2 | Nat Semi TX1 on IR TX |

| 2-3 | ARM9 TX2 on IR TX |

LK16 - IR RX Select

| Position | Description |

|---|

| 1-2 | Nat Semi RX1 on IR RX |

| 2-3 | ARM9 RX2 on IR RX |

LK17 - Nat Semi DSR1 routing

| Position | Description |

|---|

| 1-2 | Nat Semi DSR1 to IR RSL0 |

| 2-3 | Nat Semi DSR1 to COM2 DSR |

Smart Media

LK24 - NCON

| Position | Description |

|---|

| 1-2 | 4 Step Address |

| 2-3 | 3 Step Address |

LK30 - SM Address bit 0

| Position | Description |

|---|

| 1-2 | Bit 0 set |

| 2-3 | Bit 0 clear |

LK31 - SM Address bit 1

| Position | Description |

|---|

| 1-2 | Bit 1 set |

| 2-3 | Bit 1 clear |

LK32 - Smart Media Force Write Protect

| Position | Description |

|---|

| 1-2 | Write Protected |

| Open | Write Enable |

LK26 - Battery flat hold

| Position | Description |

|---|

| 1-2 | CPU held with nBAT_FLAT if SM card not present |

| Open | Normal operation |

LK27 - Smartmedia card hold

| Position | Description |

|---|

| 1-2 | hold CPU in reset if SM card not present |

| Open | Normal operation |

*NOTE* LK26/LK27 fit one only!

LK23 - Select boot device

| Position | Description |

|---|

| 1-2 | NOR flash boot |

| 2-3 | Smartmedia boot |

USB

PL2 - USB host ports

| Pin | Designation | Description |

|---|

| L1 | Supply | Lower socket +5V supply |

| L2 | D- | Lower socket data negative |

| L3 | D+ | Lower socket data positive |

| L4 | GND | Lower socket Ground |

| U1 | Supply | Upper socket +5V supply |

| U2 | D- | Upper socket data negative |

| U3 | D+ | Upper socket data positive |

| U4 | GND | Upper socket Ground |

PL6 - USB Host header

| Pin | Designation | Description |

|---|

| 1 | +5V | USB Fused and current monitored supply |

| 2 | UD- | Data - line |

| 3 | UD+ | Data + line |

| 4 | GND | Signal ground |

PL6 may be changed for a device port configuration at board manufacture time.

Test Points

| Point | Signal |

|---|

| TP4 | Davicom 20Mhz Ethernet clock |

| TP5 | 25Mhz clock Asix output |

| TP12 | I2S_CLK_OUT |