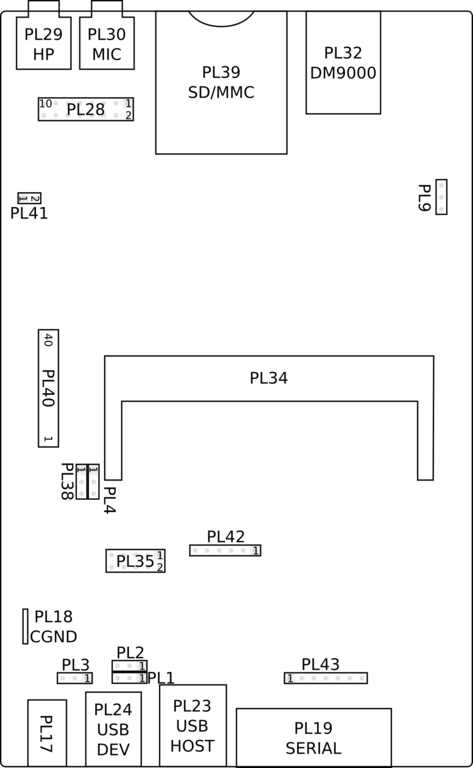

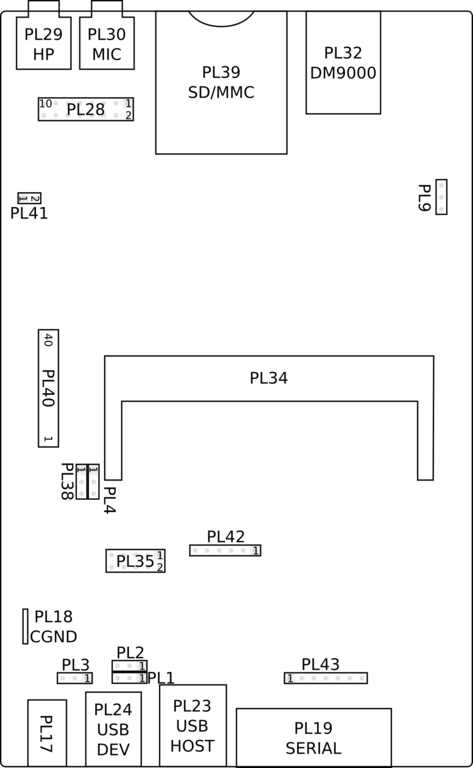

BBD20EUROU Connector/Jumper/Pinout list |

| Product | BBD20EUROU |

|---|

| Date | 16/03/2007 |

|---|

| Reference | PINLST005 |

|---|

| Author | VRS |

|---|

| Revision | 1.0 |

|---|

|

Contents

©2008 Simtec Electronics

Introduction

This document shows the pinouts for the BBD20EUROU. Several

special function pins exist which may be changed to simple GPIO if the

special function is not required. Some pins have more than one special

function which should be taken into account.

Video

PL40 - URT panel interface

| Pin | Designation | Description |

|---|

| 1 | VD<0> | D20 video bit 0 |

| 2 | N/C | Not connected |

| 3 | N/C | Not connected |

| 4 | VLED | LED backlight voltage 5V |

| 5 | VLED |

| 6 | VLED |

| 7 | VLCD | LCD display electronics supply 3.3V |

| 8 | N/C | Not connected |

| 9 | DE | D20 video DE |

| 10 | ADC<6> | Touchscreen X Left |

| 11 | ADC<5> | Touchscreen Y Up |

| 12 | TOUT<1> | D20 first TOUT |

| 13 | VD<7> | D20 video bit 7 |

| 14 | VD<6> | D20 video bit 6 |

| 15 | VD<5> | D20 video bit 5 |

| 16 | GND | Signal ground |

| 17 | VD<4> | D20 video bit 4 |

| 18 | VD<3> | D20 video bit 3 |

| 19 | VD<7> | D20 video bit 7 |

| 20 | GND | Signal ground |

| 21 | VD<15> | D20 video bit 15 |

| 22 | VD<14> | D20 video bit 14 |

| 23 | VD<13> | D20 video bit 13 |

| 24 | GND | Signal ground |

| 25 | VD<12> | D20 video bit 12 |

| 26 | VD<11> | D20 video bit 11 |

| 27 | VD<10> | D20 video bit 10 |

| 28 | GND | Signal ground |

| 29 | VD<23> | D20 video bit 23 |

| 30 | VD<22> | D20 video bit 22 |

| 31 | VD<21> | D20 video bit 21 |

| 32 | GND | Signal ground |

| 33 | VD<20> | D20 video bit 20 |

| 34 | VD<19> | D20 video bit 19 |

| 35 | VD<23> | D20 video bit 23 |

| 36 | ADC<7> | Touchscreen X Right |

| 37 | ADC<4> | Touchscreen Y Down |

| 38 | VCLK | D20 video clock |

| 39 | GND | Signal ground |

| 40 | VD<1> | D20 video bit 1 |

General IO

PL39 - SD/MMC socket

| Pin | Designation | Description |

|---|

| 1 | DATA<1> | Data bit 1 |

| 2 | DATA<0> | Data bit 0 |

| 3 | CLOCK | Data clock |

| 4 | VCC | Supply |

| 5 | GND | Signal ground |

| 6 | VCC | Supply |

| 7 | CMD | Command select |

| 8 | DATA<3> | Data bit 3 |

| 9 | DATA<2> | Data bit 2 |

PL43 - Radio

| Pin | Designation | Description |

|---|

| 1 | TX | Radio module transmit (D20 serial RX<1> ) |

| 2 | RX | Radio module recieve (D20 serial TX<1> ) |

| 3 | nPGM | Radio module MISO (D20 EINT<15>) |

| 4 | 3.3V | 3.3V supply |

| 5 | WP | Radio module WP |

| 6 | GND | Signal ground |

| 7 | nRESET | Radio module reset (D20 EINT<16>) |

Networking

PL32 - Davicom Ethernet port

| Pin | Designation | Description |

|---|

| 1 | DMTX+ | Transmit positive |

| 2 | DMTX- | Transmit negative |

| 3 | DMRX+ | Receive positive |

| 4 | N/C | No connection |

| 5 | N/C | No connection |

| 6 | DMRX- | Receive Negative |

| 7 | N/C | No connection |

| 8 | N/C | No connection |

Audio

PL41 - Amplified speaker header

| Pin | Designation | Description |

|---|

| 1 | PO+ | Speaker positive |

| 2 | PO- | Speaker negative |

PL28 - Audio Expansion

| Pin | Designation | Description |

|---|

| 1 | MIC IN | Microphone input |

| 2 | GND | Microphone ground |

| 3 | Line in left | Left line in |

| 4 | GND | Line in ground |

| 5 | Line in right | Right line in |

| 6 | GND | Line in ground |

| 7 | Line out Left | Left line out |

| 8 | GND | Line out ground |

| 9 | Line out Right | Right line out |

| 10 | GND | Line out ground |

| 11 | Headphone left out | Amplified headphone left channel |

| 12 | GND | Headphone ground |

| 13 | Headphone out right | Amplified headphone right channel |

| 14 | GND | Headphone ground |

| 15 | Supply | 5V supply |

| 16 | GND | Supply ground |

PL30 - MIC in

| Pin | Designation | Description |

|---|

| 1 | GND | Microphone ground |

| 2 | N/C | Not connected |

| 3 | N/C | Not connected |

| 4 | N/C | Not connected |

| 5 |

MIC_IN |

Input for a condensing microphone. |

PL29 - Headphones out

| Pin | Designation | Description |

|---|

| 1 | GND | Headphone ground |

| 2 | HP_RIGHT | Headphone right |

| 3 | SPKR passthrough | Right speaker pass through |

| 4 | SPKR passthrough | Left speaker pass through |

| 5 | HP_LEFT | Headphone left |

Power

PL17 - Power connector

This connector is a 2.1mm barrel jack, the center is positive

supply 4A@5V absolute maximum.

| Pin | Designation | Description |

|---|

| 1 | GND | Supply ground outer ring |

| 2 | GND | Supply Ground |

| 3 | POWER_IN | 5V Supply on center tip |

PL18 - Chassis ground spade connector

| Pin | Designation | Description |

|---|

| 1 | GND | Chassis ground point |

PL9 - Signal Ground

| Pin | Designation | Description |

|---|

| 1 | GND | Signal ground |

| 2 | GND | Signal ground |

| 3 | GND | Signal ground |

PL3 - 5V select

This link selects the 5V source of the board.

| Pin | Designation | Description |

|---|

| 1 | VUSB | USB device port 5V input |

| 2 | PSEL | Selected 5V supply into system |

| 3 | PWRJACK | Input from PL17 |

PL4 - 3.3V select

This link selects the boards 3.3V supply from between the D20

module DC-DC convertor and an onboard linear regulator.

| Pin | Designation | Description |

|---|

| 1 | D203V | D20 module 3V output. |

| 2 | 3.3V | Board 3.3V rail. |

| 3 | REG3V3 | 3.3V from regulator. |

PL38 - Module supply select

This link selects between the 3.3V and 5V supply as input to

the D20 module. If PL4 has the D203V supply

selected this link cannot have the 3.3V supply selected.

| Pin | Designation | Description |

|---|

| 1 | 5V | 5V supply |

| 2 | D20SUP | D20 supply |

| 3 | 3.3V | 3.3V supply |

Debug

PL35 - JTAG

| Pin | Designation | Description |

|---|

| 1 | 3.3V | 3.3 Volt supply |

| 2 | nTRST | Inverted tap reset |

| 3 | TDI | Tap data in |

| 4 | TMS | Tap |

| 5 | TCK | Tap clock |

| 6 | RCLK | Returned clock |

| 7 | TDO | Tap data out |

| 8 | nSRST | Inverted system reset |

| 9 | GND | Signal ground |

| 10 | NC | No connection |

Serial

PL19 - Serial Port

| Pin | Designation | Description |

|---|

| 1 | N/C | No connection |

| 2 | RX<0> | D20 port 0 Receive |

| 3 | TX<0> | D20 port 0 Transmit |

| 4 | N/C | No connection |

| 5 | GND | Ground |

| 6 | N/C | no connction |

| 7 | RTS<0> | D20 port 0 Request to send |

| 8 | CTS<0> | D20 port 0 Clear to send |

| 9 | N/C | No connection |

PL42 - Serial SIL header

| Pin | Designation | Description |

|---|

| 1 | 3.3V | 3.3V supply |

| 2 | TX<1> | D20 port 1 Transmit |

| 3 | RX<1> | D20 port 1 Receive |

| 4 | TX<2> | D20 port 2 Transmit |

| 5 | RX<2> | D20 port 2 Receive |

| 6 | GND | Signal ground |

The port 1 signals are also present as part of the PL43 radio module programming header.

USB

The D20 module provides two USB ports. The first port (port

1) is a host controller only port and is wired to the lower

socket on the dual A connector PL23. The

second port (port2) may be configured as either a host or device

port. The port is link selectable (PL1 and PL2) between the upper socket on PL23 and the type B device port connector PL24

PL1 - USB socket select

| Pin | Designation | Description |

|---|

| 1 | HD2N | PL23 upper socket. |

| 2 | DN<1> | D20 USB port 2 negative |

| 3 | DPN | PL24 device socket. |

PL2 - USB socket select

| Pin | Designation | Description |

|---|

| 1 | HD2P | PL23 upper socket. |

| 2 | DP<1> | D20 USB port 2 positive |

| 3 | DPP | PL24 device socket. |

PL23 - USB host ports

| Pin | Designation | Description |

|---|

| L1 | Supply | Lower socket +5V supply |

| L2 | D- | Lower socket data negative |

| L3 | D+ | Lower socket data positive |

| L4 | GND | Lower socket Ground |

| U1 | Supply | Upper socket +5V supply |

| U2 | D- | Upper socket data negative |

| U3 | D+ | Upper socket data positive |

| U4 | GND | Upper socket Ground |

PL24 - USB device port

| Pin | Designation | Description |

|---|

| 1 | Supply | +5V supply |

| 2 | D- | data negative |

| 3 | D+ | data positive |

| 4 | GND | Ground |

D20

PL34 - D20 connector

| Pin | Signal | Description |

|---|

| 1 | VOUT | Output supply from module |

| 2 | GND | Ground |

| 3 | nFRE | Inverted read enable |

| 4 | ALE | NAND address latch enable |

| 5 | nFWE | NAND Inverted write enable |

| 6 | CLE | NAND Command latch enable |

| 7 | nFCE<2> | Third NAND chip select |

| 8 | R/nB | NAND ready/not busy |

| 9 | D<0> | Data bus bit 0 |

| 10 | D<16> | Data bus bit 16 |

| 11 | D<1> | Data bus bit 1 |

| 12 | D<17> | Data bus bit 17 |

| 13 | D<2> | Data bus bit 2 |

| 14 | D<18> | Data bus bit 18 |

| 15 | D<3> | Data bus bit 3 |

| 16 | D<19> | Data bus bit 19 |

| 17 | D<4> | Data bus bit 4 |

| 18 | D<20> | Data bus bit 20 |

| 19 | D<5> | Data bus bit 5 |

| 20 | D<21> | Data bus bit 21 |

| 21 | D<6> | Data bus bit 6 |

| 22 | D<22> | Data bus bit 22 |

| 23 | D<7> | Data bus bit 7 |

| 24 | D<23> | Data bus bit 23 |

| 25 | D<8> | Data bus bit 8 |

| 26 | D<24> | Data bus bit 24 |

| 27 | D<9> | Data bus bit 9 |

| 28 | D<25> | Data bus bit 25 |

| 29 | D<10> | Data bus bit 10 |

| 30 | D<26> | Data bus bit 26 |

| 31 | D<11> | Data bus bit 11 |

| 32 | D<27> | Data bus bit 27 |

| 33 | D<12> | Data bus bit 12 |

| 34 | D<28> | Data bus bit 28 |

| 35 | D<13> | Data bus bit 13 |

| 36 | D<29> | Data bus bit 29 |

| 37 | D<14> | Data bus bit 14 |

| 38 | D<30> | Data bus bit 30 |

| 39 | D<15> | Data bus bit 15 |

| 40 | D<31> | Data bus bit 31 |

| 41 | GND | Ground |

| 42 | GND | Ground |

| 43 | nWBE<0> | First inverted write byte enable |

| 44 | BUF_EN | Buffer enable |

| 45 | nWBE<1> | Second inverted write byte enable |

| 46 | BUF_DIR | Buffer direction |

| 47 | nWBE<2> | Third inverted write byte enable |

| 48 | PWN_EN | Power good output |

| 49 | nWBE<3> | Forth inverted write byte enable |

| 50 | nRESET | Inverted reset output |

| 51 | nWAIT | Inverted I/O wait signal |

| 52 | nCS<1> | First inverted chip select |

| 53 | nIOCS16 | Inverted sixteen bit access select |

| 54 | nCS<2> | Second inverted chip select |

| 55 | nRD | Inverted read select |

| 56 | nCS<3> | Third inverted chip select |

| 57 | nWR | Inverted write select |

| 58 | nCS<4> | Fourth inverted chip select |

| 59 | GND | Ground |

| 60 | nCS<5> | Fifth inverted chip select |

| 61 | A<0> | Address bus bit 0 |

| 62 | A<15> | Address bus bit 15 |

| 63 | A<1> | Address bus bit 1 |

| 64 | A<16> | Address bus bit 16 |

| 65 | A<2> | Address bus bit 2 |

| 66 | A<17> | Address bus bit 17 |

| 67 | A<3> | Address bus bit 3 |

| 68 | A<18> | Address bus bit 18 |

| 69 | A<4> | Address bus bit 4 |

| 70 | A<19> | Address bus bit 19 |

| 71 | A<5> | Address bus bit 5 |

| 72 | A<20> | Address bus bit 20 |

| 73 | A<6> | Address bus bit 6 |

| 74 | A<21> | Address bus bit 21 |

| 75 | A<7> | Address bus bit 7 |

| 76 | A<22> | Address bus bit 22 |

| 77 | A<8> | Address bus bit 8 |

| 78 | A<23> | Address bus bit 23 |

| 79 | A<9> | Address bus bit 9 |

| 80 | A<24> | Address bus bit 24 |

| 81 | A<10> | Address bus bit 10 |

| 82 | A<25> | Address bus bit 25 |

| 83 | A<11> | Address bus bit 11 |

| 84 | A<26> | Address bus bit 26 |

| 85 | A<12> | Address bus bit 12 |

| 86 | TCLK0 | Timer 0 output |

| 87 | A<13> | Address bus bit 13 |

| 88 | TOUT<0> | First PWM output |

| 89 | A<14> | Address bus bit 14 |

| 90 | TOUT<1> | Second PWM output |

| 91 | GND | Ground |

| 92 | TOUT<2> | Third PWM output |

| 93 | DACK<0> | First DMA acknowledge |

| 94 | TOUT<3> | Fourth PWM output |

| 95 | DREQ<0> | First DMA request |

| 96 | DACK<1> | Second DMA acknowledge |

| 97 | I2S_LRCK | I2S left right select |

| 98 | DREQ<1> | Second DMA request |

| 99 | I2S_CLK | I2S clock |

| 100 | EINT<0> | External interrupt 0 |

| 101 | I2S_CDCLK | I2S command/data select |

| 102 | EINT<1> | External interrupt 1 |

| 103 | I2S_SDI | I2S serial data in |

| 104 | EINT<2> | External interrupt 2 |

| 105 | I2S_SDO | I2S serial data out |

| 106 | EINT<3> | External interrupt 3 |

| 107 | SDCLK | SD card clock |

| 108 | EINT<4> | External interrupt 4 |

| 109 | SDCMD | SD card command |

| 110 | EINT<5> | External interrupt 5 |

| 111 | SDDATA<0> | SD card first data line |

| 112 | EINT<6> | External interrupt 6 |

| 113 | SDDATA<1> | SD card second data line |

| 114 | EINT<7> | External interrupt 7 |

| 115 | SDDATA<2> | SD card third data line |

| 116 | EINT<8> | External interrupt 8 |

| 117 | SDDATA<3> | SD card fourth data line |

| 118 | EINT<9> | External interrupt 9 |

| 119 | SPIMISO | SPI bus master in slave out |

| 120 | EINT<10> | External interrupt 10 |

| 121 | SPIMOSI | SPI bus master out slave in |

| 122 | EINT<11> | External interrupt 11 |

| 123 | SPICLK | SPI bus clock |

| 124 | EINT<12> | External interrupt 12 |

| 125 | SCL | I2C bus clock |

| 126 | EINT<13> | External interrupt 13 |

| 127 | SDA | I2C bus data |

| 128 | EINT<14> | External interrupt 14 |

| 129 | GND | Ground |

| 130 | EINT<15> | External interrupt 15 |

| 131 | LEND | Line end |

| 132 | EINT<16> | External interrupt 16 |

| 133 | VCLK | Video clock |

| 134 | RTS<1> | Second serial port request to send |

| 135 | HS | Horizontal sync |

| 136 | CTS<1> | Second serial port clear to send |

| 137 | VS | Vertical sync |

| 138 | EINT<19> | External interrupt 19 |

| 139 | DE/VM | Video data enable |

| 140 | CTS<0> | First serial port Clear To Send |

| 141 | VD<0> | Video bus bit 0 |

| 142 | RTS<0> | First serial port Request To Send |

| 143 | VD<1> | Video bus bit 1 |

| 144 | TX<0> | First serial port transmit |

| 145 | VD<2> | Video bus bit 2 |

| 146 | RX<0> | First serial port recive |

| 147 | VD<3> | Video bus bit 3 |

| 148 | TX<1> | Second serial port transmit |

| 149 | VD<4> | Video bus bit 4 |

| 150 | RX<1> | Second serial port recive |

| 151 | VD<5> | Video bus bit 5 |

| 152 | TX<2> | Third serial port transmit |

| 153 | VD<6> | Video bus bit 6 |

| 154 | RX<1> | Third serial port recive |

| 155 | VD<7> | Video bus bit 7 |

| 156 | VOUT | Output supply from module |

| 157 | VD<8> | Video bus bit 8 |

| 158 | GND | Analog Ground |

| 159 | VD<9> | Video bus bit 9 |

| 160 | ADC<0> | Analog input 0 |

| 161 | VD<10> | Video bus bit 10 |

| 162 | ADC<1> | Analog input 1 |

| 163 | VD<11> | Video bus bit 11 |

| 164 | ADC<2> | Analog input 2 |

| 165 | VD<12> | Video bus bit 12 |

| 166 | ADC<3> | Analog input 3 |

| 167 | VD<13> | Video bus bit 13 |

| 168 | ADC<4> | Analog input 4 |

| 169 | VD<14> | Video bus bit 14 |

| 170 | ADC<5> | Analog input 5 |

| 171 | VD<15> | Video bus bit 15 |

| 172 | ADC<6> | Analog input 6 |

| 173 | VD<16> | Video bus bit 16 |

| 174 | ADC<7> | Analog input 7 |

| 175 | VD<17> | Video bus bit 17 |

| 176 | GND | Ground |

| 177 | VD<18> | Video bus bit 18 |

| 178 | DN<0> | Data negative for USB port 0 |

| 179 | VD<19> | Video bus bit 19 |

| 180 | DP<0> | Data positive for USB port 0 |

| 181 | VD<20> | Video bus bit 20 |

| 182 | DN<1> | Data negative for USB port 0 |

| 183 | VD<21> | Video bus bit 21 |

| 184 | DP<1> | Data positive for USB port 1 |

| 185 | VD<22> | Video bus bit 22 |

| 186 | nTRST | Inverted tap reset |

| 187 | VD<23> | Video bus bit 23 |

| 188 | TDI | Tap data input |

| 189 | GND | Ground |

| 190 | TMS | Tap mode select |

| 191 | VCC_RTC | Real time clock supply |

| 192 | TCK | Tap clock |

| 193 | VIN | Power supply |

| 194 | TDO | Tap data out |

| 195 | VIN | Power supply |

| 196 | nRESET | Inverted reset input |

| 197 | VIN | Power supply |

| 198 | GND | Ground |

| 199 | VIN | Power supply |

| 200 | GND | Ground |